用過Allegro的讀者一定知道,Allegro中有大量的顏色設(shè)定命令,大量的約束條件,而且在出Gerber文件時也需要做大量的設(shè)定。在不同的PCB設(shè)計中,這些操作是類似的,重復(fù)的,因此,如果能夠建立PCB設(shè)計模板,將會大幅提升工作效率,并降低出錯的概率。本文針對這一過程做簡單闡述。

1. 創(chuàng)建一個空的PCB文件。運行Allegro,點擊File—>New,在彈出的對話框中選擇Board,如下圖。

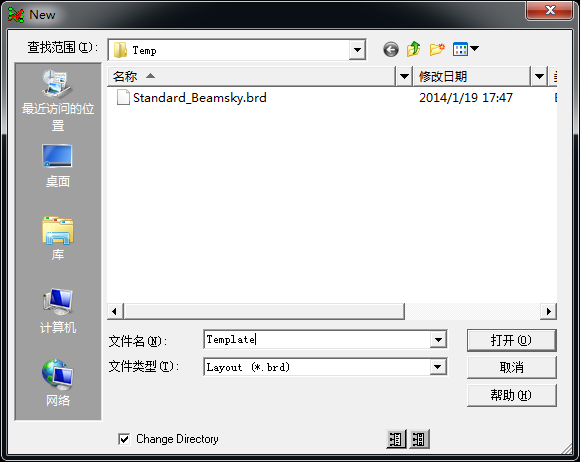

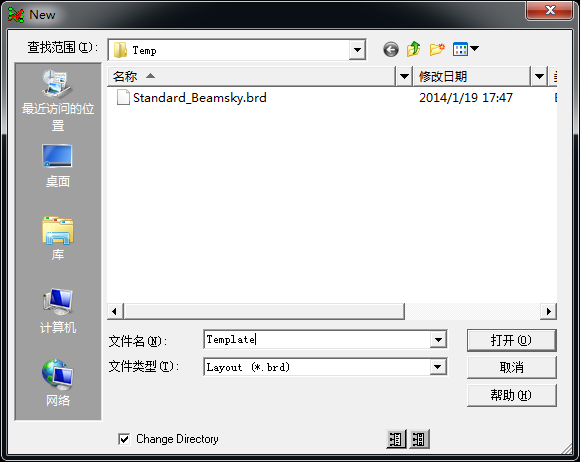

點擊Browse,找到欲存放PCB文件的目錄,本例中是E:/Temp目錄下,并在彈出的對話框中輸入文件名Template,如下圖。

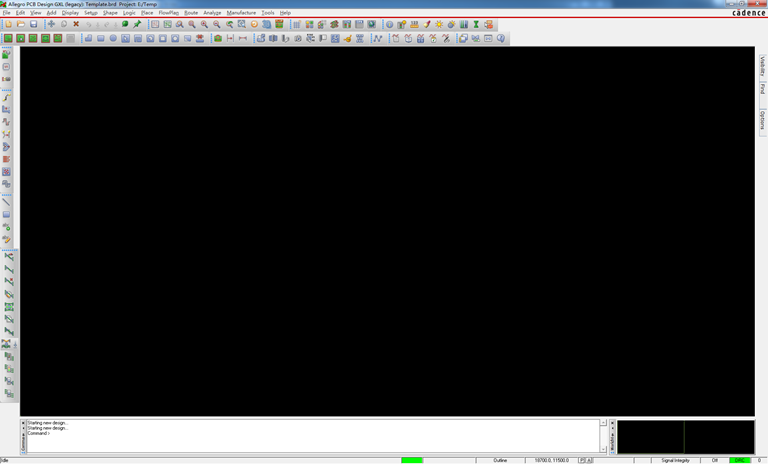

點擊打開后,Allegro就創(chuàng)建完成了一個空的PCB文件,此時回到主界面,如下圖。

2. 變更PCB疊層。Allegro創(chuàng)建的PCB默認是2層板的,如下圖。

2層板顯然不符合一般的產(chǎn)品設(shè)計要求,在此將其變更為8層板,按照下圖方式進行設(shè)置。

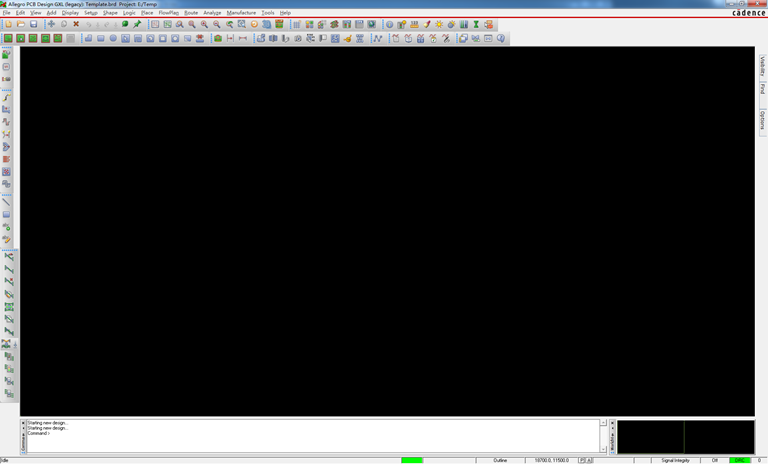

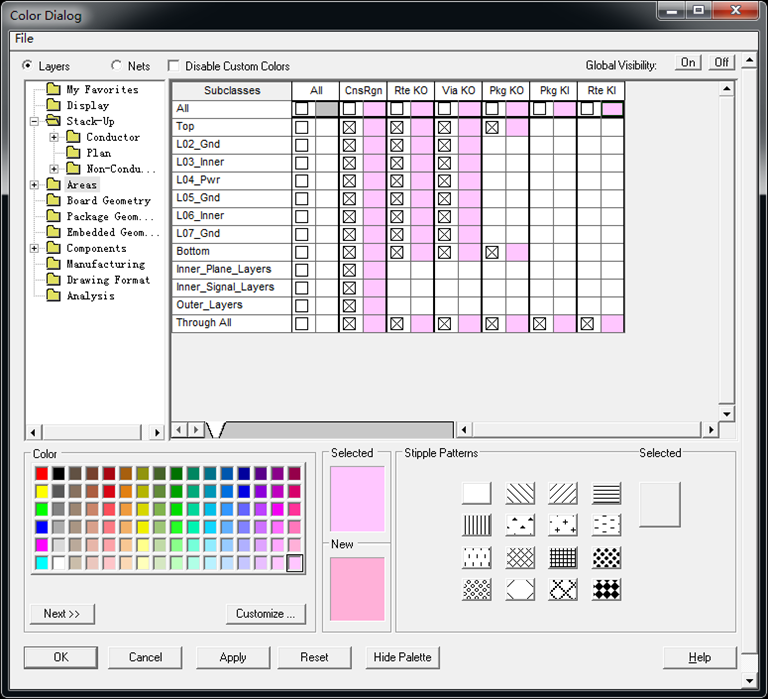

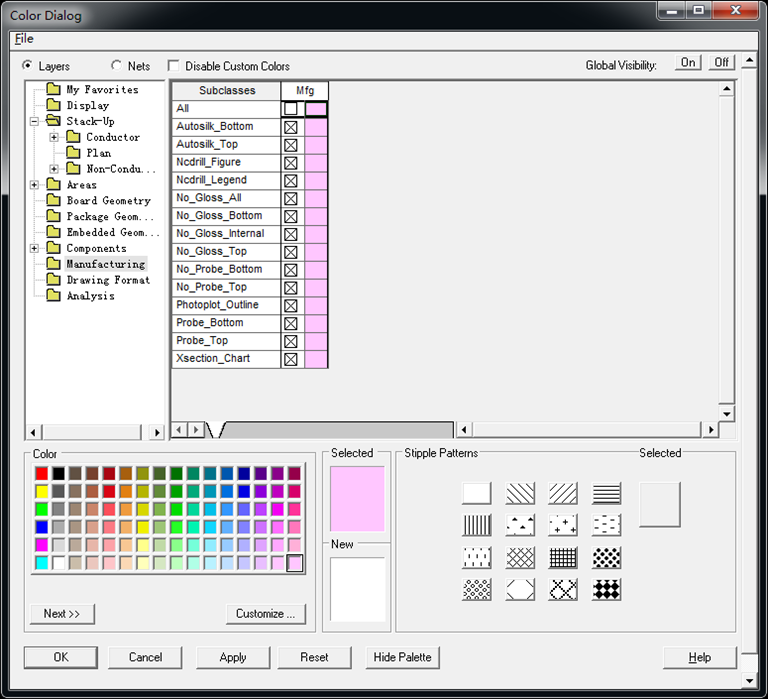

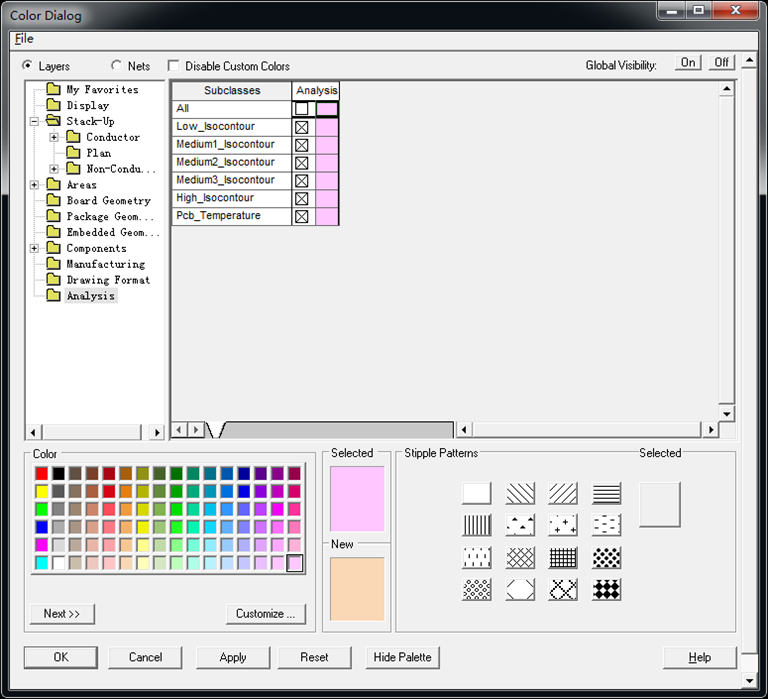

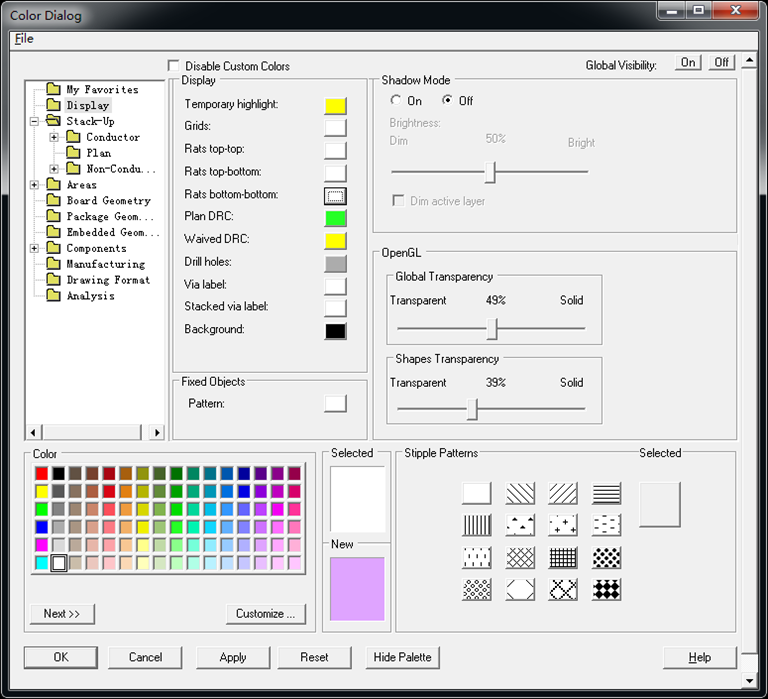

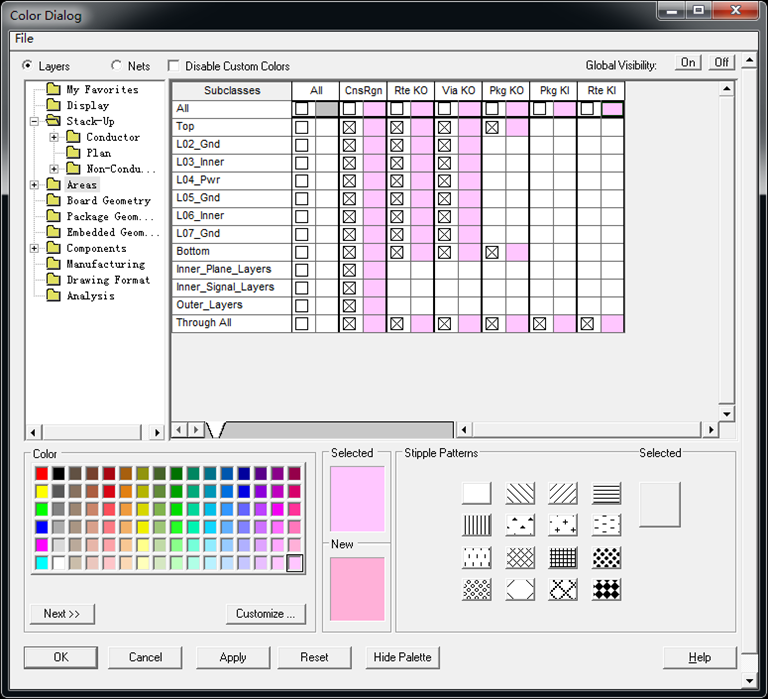

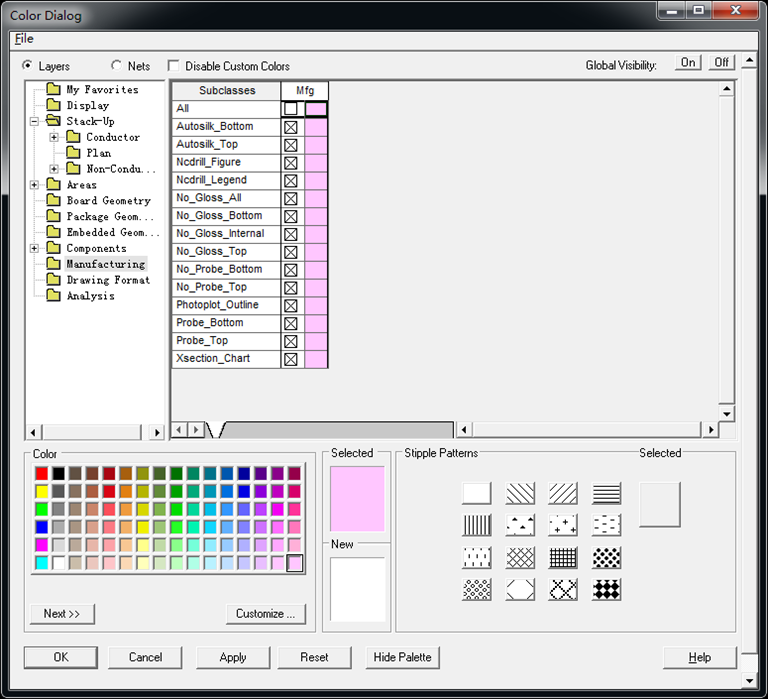

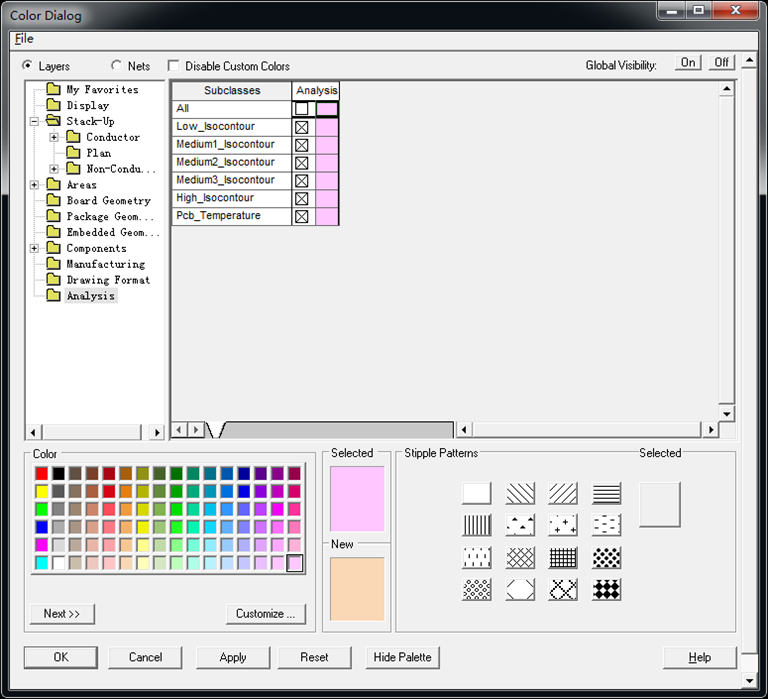

3. 變更顏色設(shè)定。Allegro中默認的顏色設(shè)定是大片的綠色,不知道各位讀者是否習(xí)慣, 筆者本人是不太喜歡這樣的設(shè)定。此處可根據(jù)個人習(xí)慣進行更改,以下圖片是 筆者設(shè)置完成的顏色設(shè)定。

Display

Stack-Up

Areas

Board Geometry

Package Geometry

Components

Manufacturing

Drawing Format

Analysis

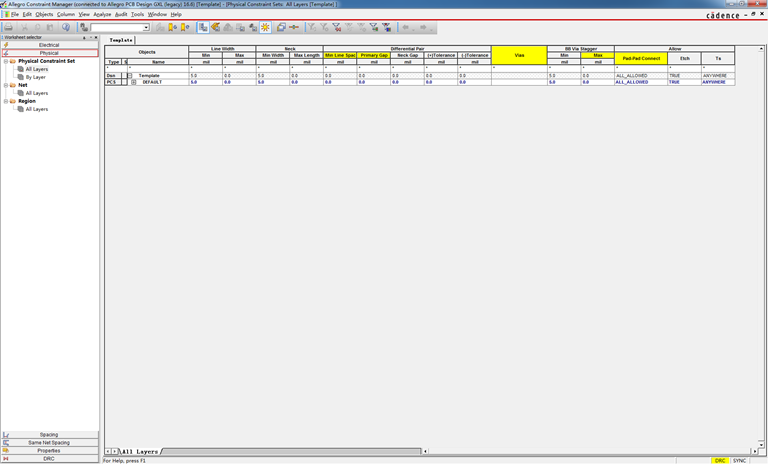

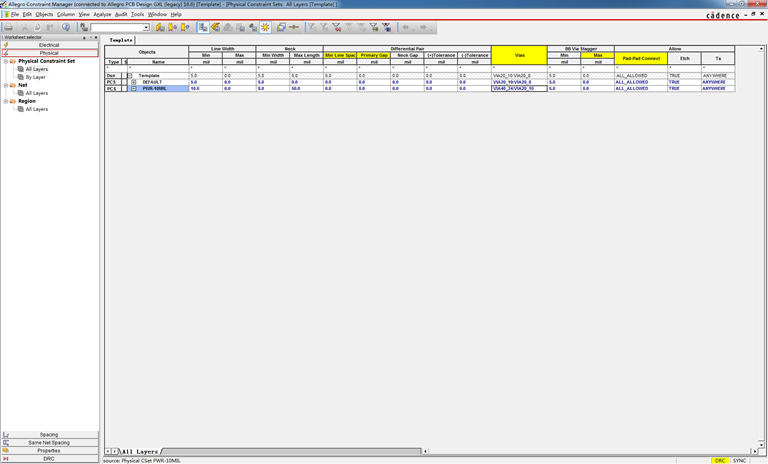

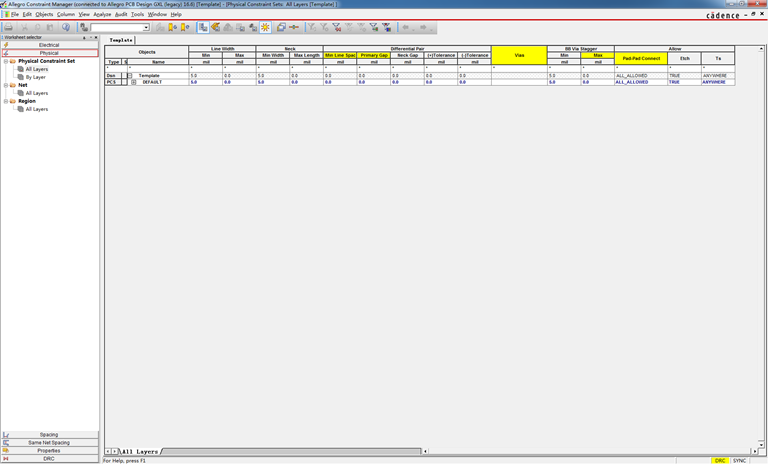

4. 變更約束條件。本文僅針對約束條件中的Physical屬性變更做簡要說明,Allegro默認的Physical屬性如下圖。

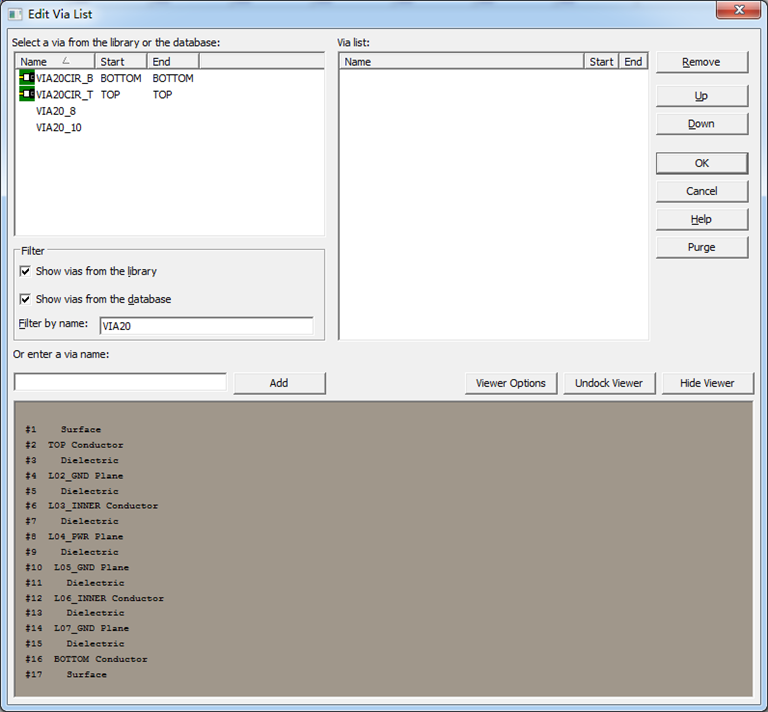

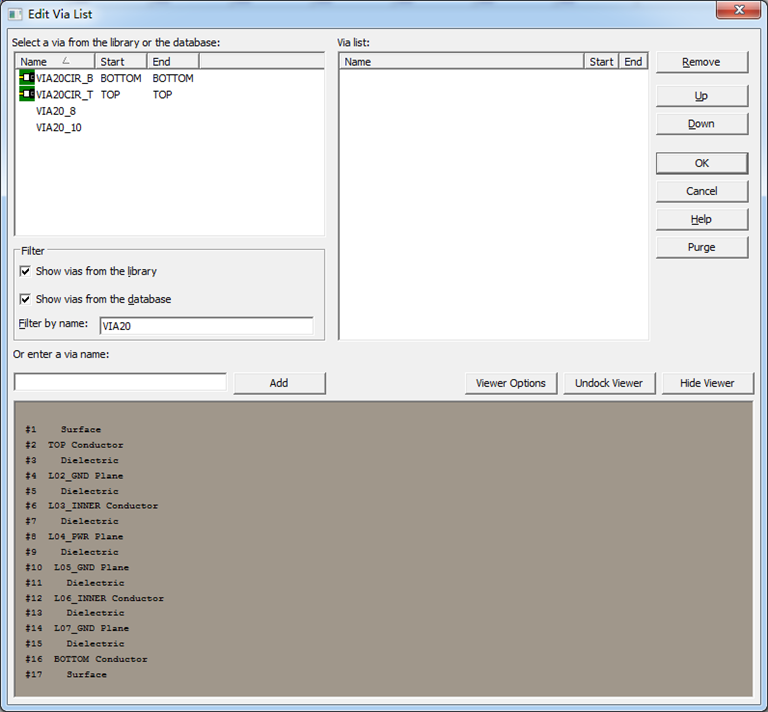

指定所使用的過孔。單擊DEFAULT一行與Vias一列的交叉位置處,會彈出Edit Via List對話框,如下圖。

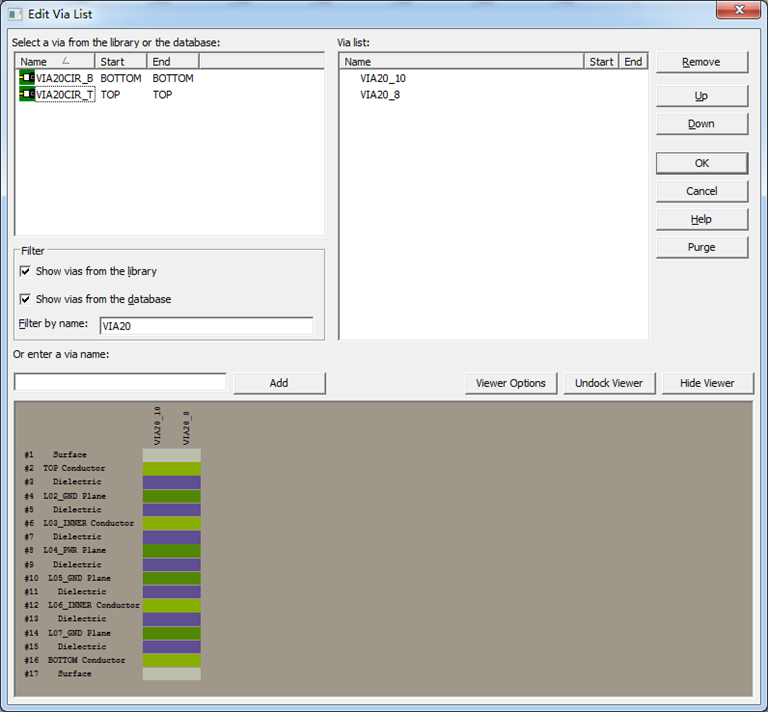

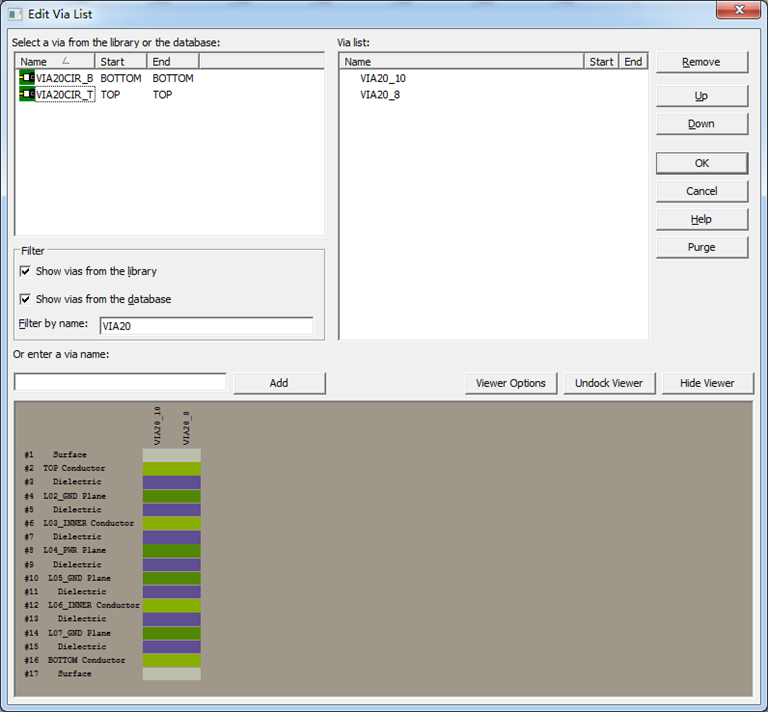

可以在Filter by name一欄中輸入過孔名稱進行過濾,如輸入VIA20就會出現(xiàn)以VIA20*作為名稱的全部過孔,包括VIA20CIR_B,VIA20CIR_T,VIA20_8,VIA20_10。注意這里出現(xiàn)的過孔是 筆者本機所指定的封裝庫中已經(jīng)存在的過孔,如果讀者沒有相應(yīng)的數(shù)據(jù)庫或者未正確指定封裝庫所在路徑,則無法出現(xiàn)這些過孔。雙擊需要使用的過孔,就可以將相應(yīng)的過孔添加至右側(cè)的Via list中,如下圖。

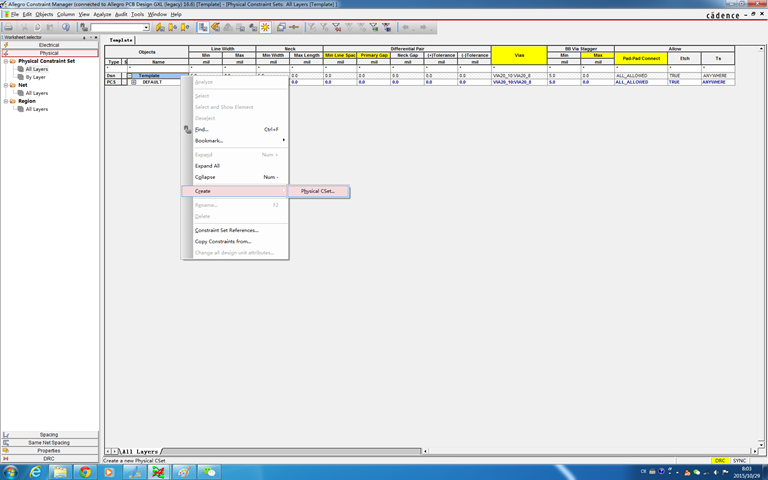

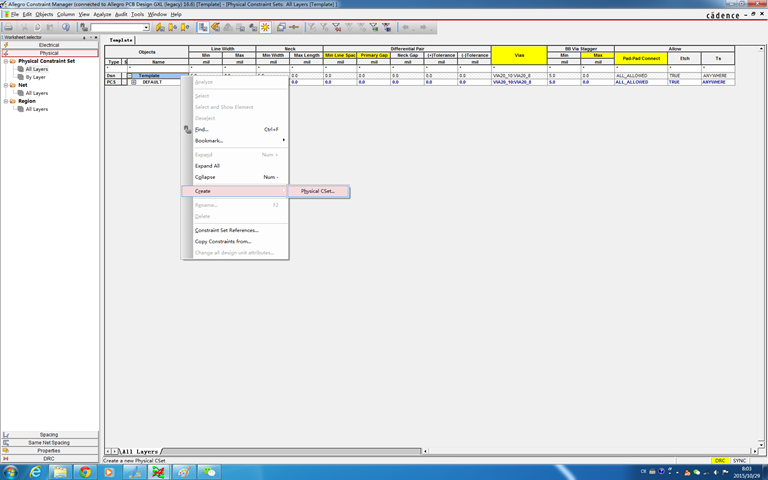

這些過孔的使用優(yōu)先順序還可以使用Up/Down命令進行調(diào)整。點擊OK返回Constain Manager主界面,再為電源網(wǎng)絡(luò)創(chuàng)建單獨的Phsical屬性。在Template上點擊右鍵,然后依次點擊Create—>Physical Cset,如下圖。

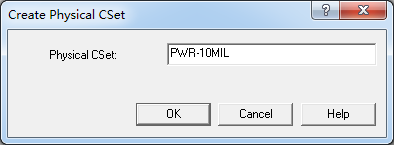

在彈出的對話框中將新的Cset命名為PWR-10MIL,如下圖。

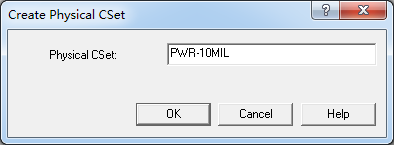

修改PWR-10MIL Cset對應(yīng)的線寬為10mil,Neck為8mil,默認過孔為VIA40_24,可選過孔為VIA20_10,如下圖。

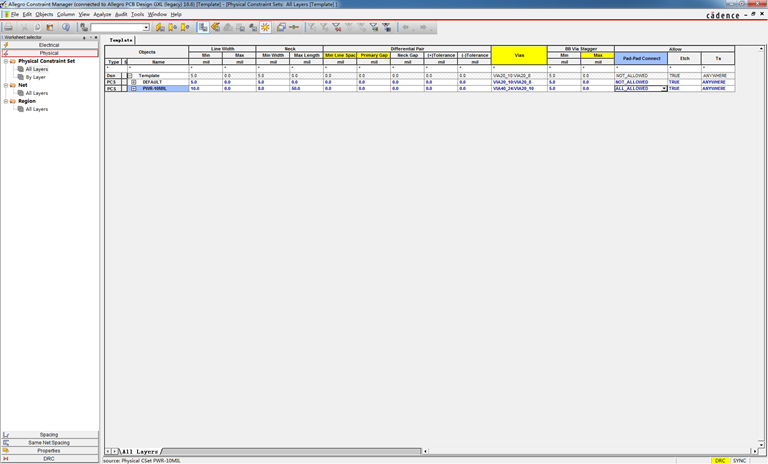

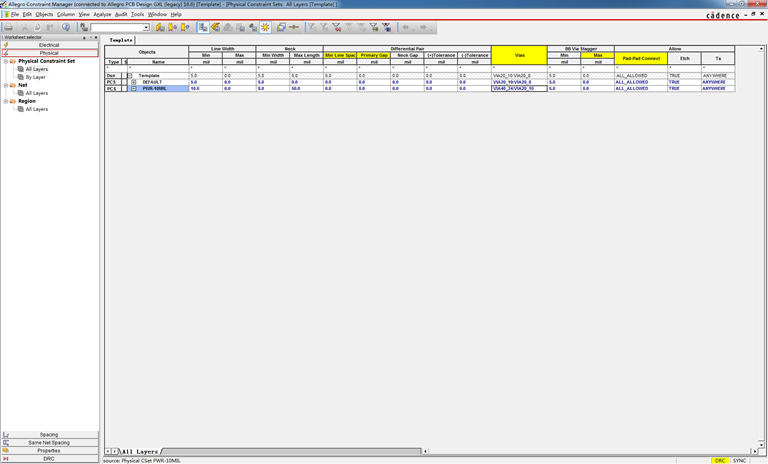

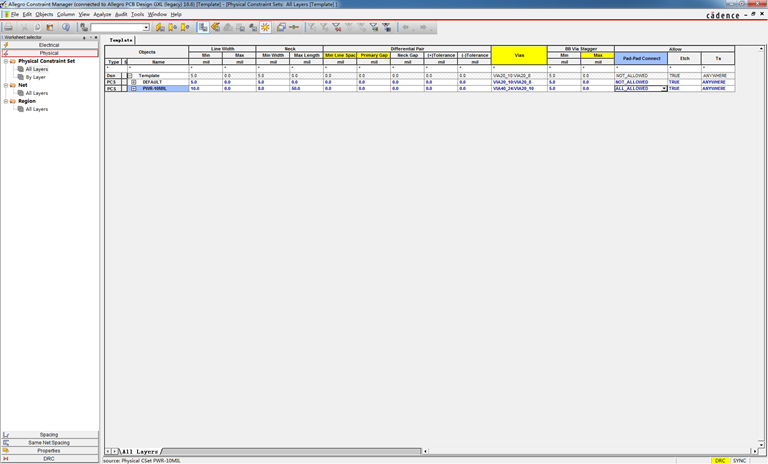

這里有一點需要指出的是,通常的PCB設(shè)計不允許過孔打在焊盤上,但對于芯片底部存在較大接地焊盤的情況,則不可避免,為了滿足這樣的條件,將DEFAULT對應(yīng)的Pad-Pad Connect變更為Not Allowed,PWR-10MIL對應(yīng)的Pad-Pad Connect變更為All Allowed,如下圖。

Electrical的約束條件的設(shè)定只能是在網(wǎng)表導(dǎo)入之后進行,其他約束條件的設(shè)定讀者可自行研究,可根據(jù)實際PCB設(shè)計規(guī)范,制板工藝等進行調(diào)整。

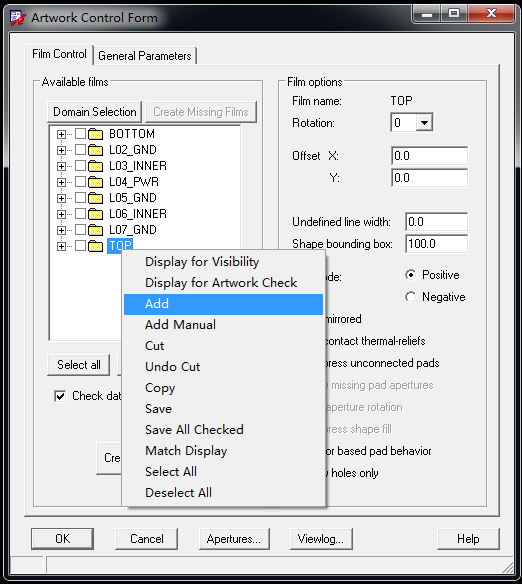

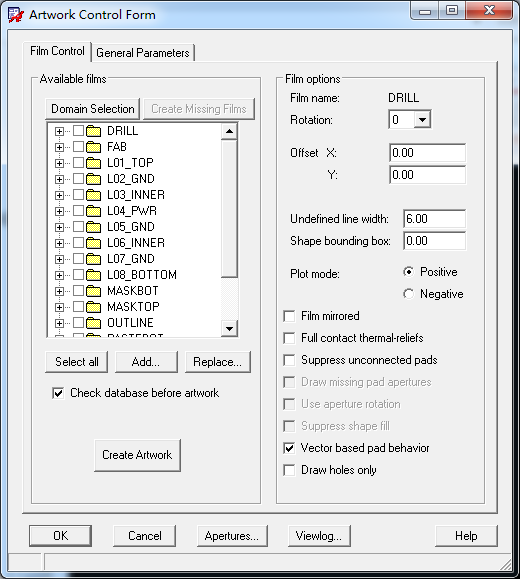

5. 設(shè)置Gerber文件。點擊工具欄中的“照相機”圖標,會彈出Artwork Control Form窗口,如下圖。

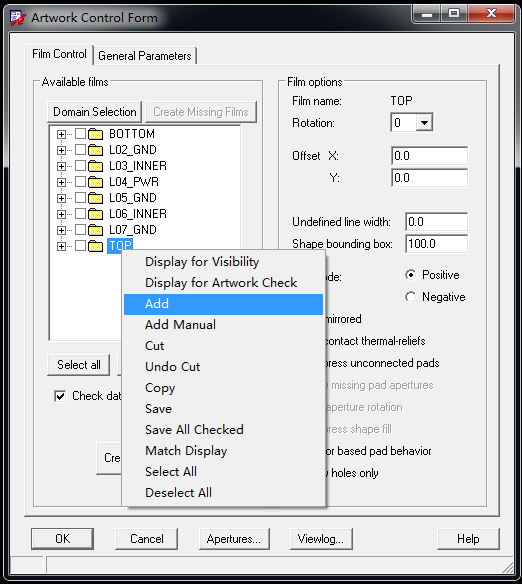

顯然,如果只將這些Film輸出是不夠的。本文以頂層絲印為例,闡述增加輸出Film的方法。在任意Film上面點擊右鍵—>Add,如下圖。

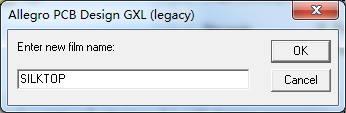

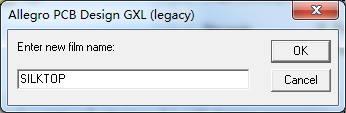

在彈出的對話框中輸入新的Film名稱SILKTOP,如下圖。

Artwork Control Form窗口,展開SILKTOP文件夾,發(fā)現(xiàn)其中出現(xiàn)了大量的層,如下圖。

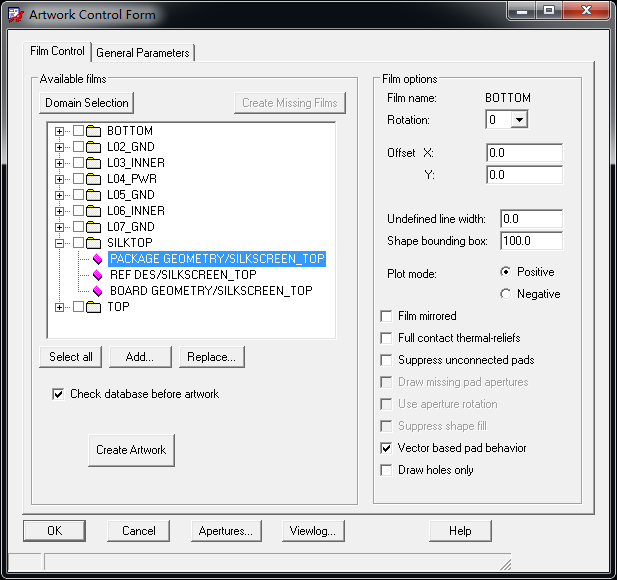

將其逐個刪除,并添加PACKAGE GEOMETRY中的SILKSCREEN_TOP,REF DES中的SILKSCREEN_TOP,BOARD_GEOMETRY中的SILKSCREEN_TOP,完成后如下圖。

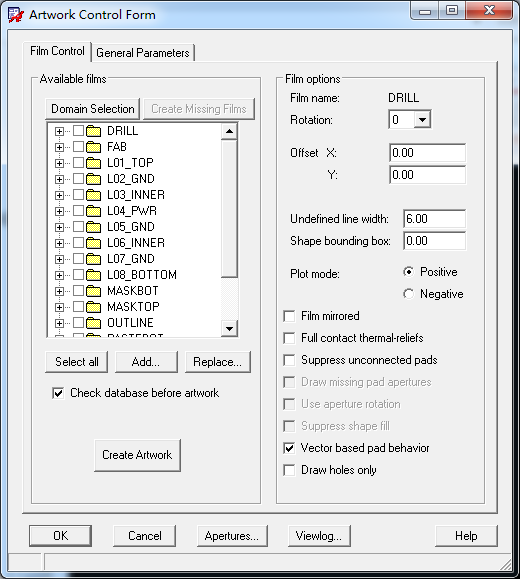

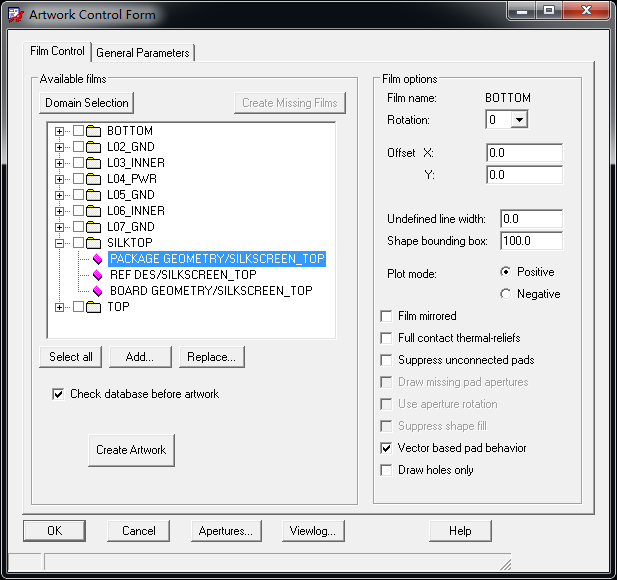

按照類似方式,添加Soldermask,Pastemask,Outline等Film,完成后的設(shè)定如下圖。

6. 其他設(shè)定。點擊Setup—>Design Parameters,變更默認設(shè)置為個人習(xí)慣,如下圖是 筆者常用的設(shè)置。

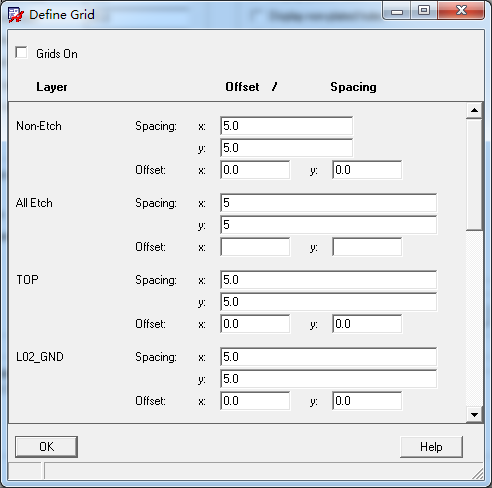

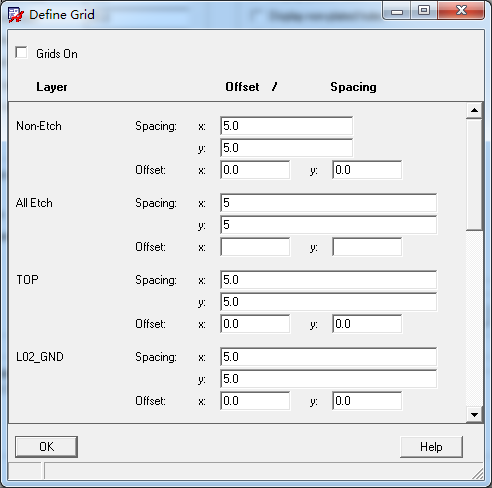

點擊Setup Grids按鈕,設(shè)置格點為5mil,如下圖。

7. 到目前為止,已經(jīng)完成了模板的建立。最后通過實際的PCB設(shè)計,對模板進行檢驗。將剛剛創(chuàng)建的Template.brd復(fù)制,命名為Test.brd。在Test.brd中隨意設(shè)定Outline,并導(dǎo)入一份網(wǎng)表,完成后的效果如下圖所示,讀者可自行檢查此前設(shè)定的規(guī)則是否正確。